## FONDAMENTI DI INFORMATICA

### Lezione n. 7

#### Esercizi di progetto di circuiti sequenziali

## ESERCIZIO N. 1

**Progettare un circuito sequenziale che moltiplicherà per tre un numero binario N di lunghezza arbitraria.**

Il numero viene acquisito in modo seriale dall'ingresso  $x$  a partire dal bit meno significativo.

La cifra che rappresenta  $3N$  deve presentarsi serialmente all'uscita  $z$  del circuito.

## SOLUZIONE ESERCIZIO N. 1

0 0 0 1 0 1 1 0 1 0 .... ingresso

0 0 0 1 0 1 1 0 1 ingresso con ritardo (ovvero bit precedente)

0 0 0 1 1 1 0 0 0 1 somma.

Data una sequenza all'ingresso la sequenza di uscita considera il valore presente (peso 1) e quello precedente (peso 2) e li somma.

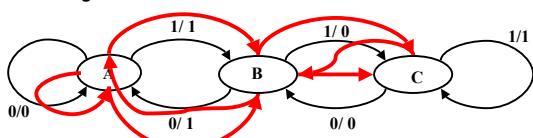

Diagramma di stato dell'evoluzione del circuito.

## ESERCIZIO N. 2

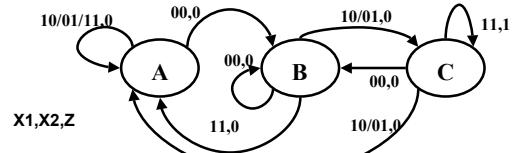

- Progettare una rete sequenziale sincrona con il compito di verificare l'andamento di due segnali di ingresso  $X_1, X_2$ . Il segnale di uscita  $Z$  avrà valore 1 quando per i due segnali di ingresso si verifica una delle seguenti evoluzioni: (00,01,11) oppure (00,10,11). L'uscita  $Z$  viene mantenuta inalterata fin tanto che permane la configurazione finale (11).

- Per la realizzazione dell'automa sono sufficienti tre stati.

- Progettare il circuito mediante FF-JK e porte logiche.

- A: la sequenza non è ancora iniziata. Si passerà allo stato B quando in ingresso compare 00.

- B: il primo elemento della sequenza è stato riconosciuto. Si passa a C quando 10 o 01 compaiono agli ingressi.

- C: il secondo elemento della sequenza è stato riconosciuto. L'uscita va finalmente a 1 quando compare il terzo elemento della sequenza.

## ESERCIZIO N. 2b

- Progettare una rete sequenziale sincrona con il compito di verificare l'andamento di due segnali di ingresso  $X_1, X_2$ . Il segnale di uscita  $Z$  avrà valore 1 quando per i due segnali di ingresso si verifica una delle seguenti evoluzioni: (00,01,11) oppure (00,10,11). Ogni passo può anche presentarsi più volte consecutivamente. L'uscita  $Z$  viene mantenuta inalterata fin tanto che permane la configurazione finale (11).

- Progettare il circuito mediante FF-JK e porte logiche.

|      |      | J1 |    |    |    |

|------|------|----|----|----|----|

| X1X2 | F0F1 | 00 | 01 | 11 | 10 |

| 00   |      | 0  | 0  | 0  |    |

| 01   |      | d  | d  | d  |    |

| 11   |      | d  | d  | d  |    |

| 10   |      | 0  | 0  | 0  |    |

$$J1 = \overline{X1} \cdot \overline{X2}$$

|      |      | K1 |    |    |    |

|------|------|----|----|----|----|

| X1X2 | F0F1 | 00 | 01 | 11 | 10 |

| 00   |      | d  |    |    |    |

| 01   |      | 0  |    |    |    |

| 11   |      | d  |    |    |    |

| 10   |      | d  |    |    |    |

$$K1 = X1 + X2$$

|      |      | Z  |    |    |    |

|------|------|----|----|----|----|

| X1X2 | F0F1 | 00 | 01 | 11 | 10 |

| 00   |      | 0  | 0  | 0  | 0  |

| 01   |      | 0  | 0  | 0  | 0  |

| 11   |      | d  | d  | d  | d  |

| 10   |      | 0  | 0  | 0  | 0  |

$$Z = F0 \cdot X1 \cdot X2$$