## FONDAMENTI DI INFORMATICA

### Lezione n. 5

- CIRCUITI COMBINATORI E CIRCUITI SEQUENZIALI

- CIRCUITI BEN FORMATI

- INTRODUZIONE AI CIRCUITI SEQUENZIALI

- ELEMENTI DI MEMORIA

In questa lezione verranno considerate le differenze tra circuiti combinatori e circuiti sequenziali e introdotti i primi elementi sui circuiti sequenziali.

## CIRCUITI COMBINATORI E SEQUENZIALI

I circuiti logici possono appartenere a due categorie:

- **CIRCUITI COMBINATORI.** Le uscite sono solo funzione del valore assunto nello stesso istante dagli ingressi.

- **CIRCUITI SEQUENZIALI.** Le variabili di uscita non dipendono solo dagli ingressi ma anche dalla storia precedente del circuito.

I circuiti sequenziali devono disporre di elementi in grado di mantenere *memoria* dello stato del sistema.

Stato: riassunto finito della storia passata.

## CIRCUITI COMBINATORI

I circuiti combinatori si dicono *well formed* (w.f.) o ben formati se si ottengono a partire da porte logiche primitive secondo le seguenti regole:

- Una singola linea o una singola porta è un circuito w.f.

- La giustapposizione di due circuiti w.f. dà origine a un circuito w.f.

## CIRCUITI COMBINATORI

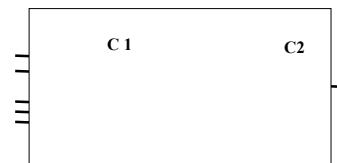

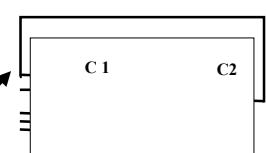

- Se  $C_1$  e  $C_2$  sono due circuiti w.f. separati, il circuito che si ottiene collegando linee di uscita di  $C_1$  con linee di ingresso di  $C_2$  è w.f.

## CIRCUITI COMBINATORI

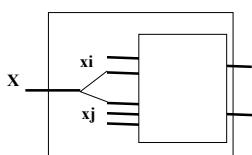

- Se  $x_i$  e  $x_j$  sono linee di ingresso di un circuito w.f. e se si collega  $x_i$  e  $x_j$  tra loro in  $X$ , si ottiene un circuito w.f.

## CIRCUITI COMBINATORI

- I circuiti combinatori w.f. non contengono anelli e le uscite non sono mai collegate fra loro.

- Eccezioni a questi comportamenti o richiedono la comprensione di meccanismi a livelli di astrazione inferiore o introducono meccanismi di memoria.

Tecnologia Elettronica.

Memoria

## CIRCUITI SEQUENZIALI

- Un circuito sequenziale dispone di elementi di memoria per ricordare la storia passata.

- Il più semplice elemento di memoria è il **FLIP-FLOP**, in grado di immagazzinare un bit di informazione per un tempo indefinito.

I FLIP-FLOP o multivibratori bistabili sono elementi circuitali in grado di:

- permanere stabili in due stati diversi (**MEMORIA**).

- commutare da uno stato all'altro (**SCRITTURA**).

- manifestare lo stato interno (**LETTURA**).

Il FLIP-FLOP costituisce una cella di memoria.

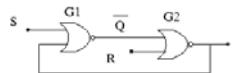

## FLIP-FLOP S-R

| S | R | Q | Q-bar | STATO      |

|---|---|---|-------|------------|

| 1 | 0 | 1 | 0     | SET        |

| 0 | 1 | 0 | 1     | RESET      |

| 0 | 0 | Q | Q-bar | MEMORIA    |

| 1 | 1 | 0 | 0     | NON VALIDO |

Funzionamento del circuito:

- **SET=1 e RESET=0.**  $\Rightarrow$  L'uscita  $\bar{Q}$  vale 0 e  $Q$  vale 1.

- **RESET=1 e SET=0.**  $\Rightarrow$  L'uscita  $Q$  vale 0 e  $\bar{Q}$  vale 1.

Ciò verifica la possibilità di scrivere 0 o 1 nell'elemento di memoria.

Se in uno qualsiasi dei due casi si porta a 0 l'ingresso che era 1 il circuito mantiene la stessa configurazione delle uscite.

Questa situazione è quella di memoria.

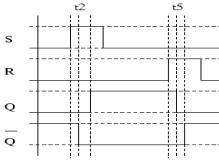

## FLIP-FLOP SR

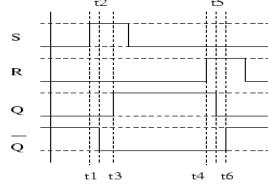

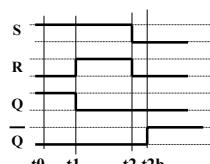

- Inizialmente  $SR=00$  e  $Q=0$ .

- Se  $S \Rightarrow 1$  allora  $\bar{Q} \Rightarrow 0$  dopo  $(t_2 - t_1)$ . Successivamente l'uscita  $Q \Rightarrow 1$  in quanto i due ingressi sono a 0.

- Quando  $S \Rightarrow 0$  il FLIP-FLOP si porta nella condizione di memoria e quindi mantiene lo stato memorizzato.

- Operazione di scrittura.

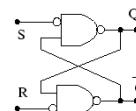

## FLIP-FLOP con porte NAND

- E' possibile realizzare un FLIP-FLOP anche con porte NAND.

| S | R | Q | Q-bar | STATO      |

|---|---|---|-------|------------|

| 1 | 0 | 1 | 0     | SET        |

| 0 | 1 | 0 | 1     | RESET      |

| 0 | 0 | Q | Q-bar | MEMORIA    |

| 1 | 1 | 0 | 0     | NON VALIDO |

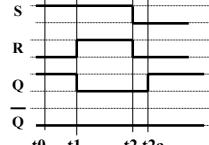

## FLIP-FLOP S-R

La condizione  $SR=11$  non è consentita e non dovrà mai comparire all'ingresso del FLIP-FLOP, in quanto:

- Forza uscite non complementari.

- La transizione  $SR=11 \Rightarrow 00$  porta a situazioni diverse in funzione del ritardo introdotto dalle singole porte.

- All'istante t2 il valore delle uscite non è definito.

## FLIP-FLOP S-R

| t0 | t1 | t2 | t2a | t2b |

|----|----|----|-----|-----|

| S  | 1  | 1  | 0   | 0   |

| R  | 0  | 1  | 0   | 0   |

| Q  | 0  | 0  | nd  | 1   |

- Nel caso t2a il ritardo introdotto dalla porta G1 è "molto" maggiore di quello introdotto dalla porta G2.

- Nel caso t2b si verifica la situazione opposta.

## CORSE CRITICHE E CLOCK

I fenomeni di questo tipo prendono il nome di **corse critiche**.

- Configurazioni non volute si presentano agli ingressi di circuiti di memoria.

- Differenze di comportamento tra i circuiti portano a evoluzioni casuali.

Per eliminare le corse critiche e per razionalizzare il progetto viene introdotto il segnale di cadenza o di **clock**.

## IL SEGNALE DI CLOCK

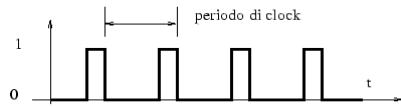

### CLOCK A LIVELLO

- Stato attivo  $\Rightarrow 1$

Vi avvengono le transizioni.

Ha la durata minima necessaria a garantire il cambiamento di stato di tutti i circuiti di memoria.

### Stato inattivo $\Rightarrow 0$

Viene consentito alla rete combinatoria di modificare le uscite.

La durata minima consente in ogni caso l'evoluzione completa della rete.

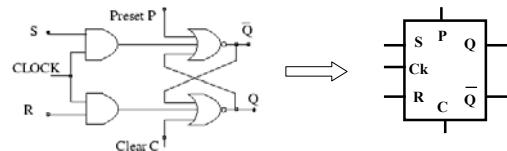

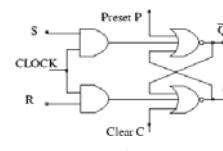

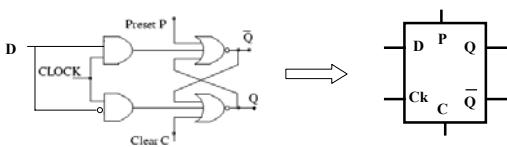

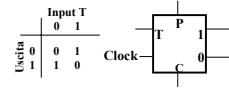

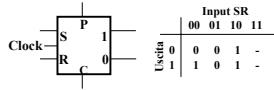

## IL FLIP-FLOP S-R CADENZATO

- Preset (P) e Clear (C):** Forzano il FF in uno dei due stati indipendentemente dal clock.

- CLOCK:** Se  $CLOCK=0$  blocca gli ingressi, lasciando evolvere il sistema. Se  $CLOCK=1$  S e R sono attivi sul FF.

## IL FLIP-FLOP S-R CADENZATO

| S | R | Ck | Q (n+1) |

|---|---|----|---------|

| X | X | 0  | Q(n)    |

| 1 | 0 | 1  | 1       |

| 0 | 1 | 1  | 0       |

| 0 | 0 | 1  | Q(n)    |

| 1 | 1 | 1  | x       |

Attenzione: i segnali di ingresso S e R non cambiano quando il segnale di CLOCK vale 1 (per definizione).

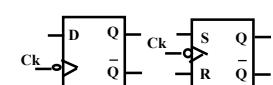

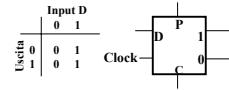

## D-LATCH

Il D-LATCH memorizza il dato presente in ingresso.

| D | Ck | Q (n+1) |

|---|----|---------|

| 1 | 1  | 1       |

| 0 | 1  | 0       |

| 1 | 0  | Q(n)    |

| 0 | 0  | Q(n)    |

## I FLIP-FLOP EDGE-TRIGGERED

- I FF attivi sul livello richiedono un circuito più complesso per la generazione del segnale di clock. (basso duty-cycle, definito come  $t_{(CK=1)}/t_{(CK=0)}$ ).

- Sono soggetti a rischio di transizioni multiple nello stesso intervallo di CLOCK.

- I FF più sicuri (FF sincroni) commutano sui fronti di salita o sui fronti di discesa del segnale di CLOCK.

FF attivi sul fronte di salita

FF attivi sul fronte di discesa

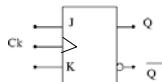

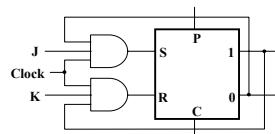

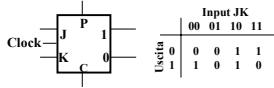

## ALTRI TIPI DI FF SINCRONI

### FLIP-FLOP J-K

Si comporta come un FLIP-FLOP S-R ma accetta in ingresso la combinazione JK=11 che inverte il valore delle uscite

| J | K | Ck | Q(n+1) |

|---|---|----|--------|

| X | X | 0  | Q(n)   |

| 1 | 0 | 1  | 1      |

| 0 | 1 | 1  | 0      |

| 0 | 0 | 1  | Q(n)   |

| 1 | 1 | 1  | Q(n)   |

## ALTRI TIPI DI FF CADENZATI

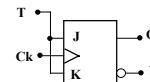

| T | J | K | Q(n+1) |

|---|---|---|--------|

| 0 | 0 | 0 | Q(n)   |

| 1 | 1 | 1 | Q(n)   |

| D | J | K | Q(n+1) |

|---|---|---|--------|

| 1 | 1 | 0 | 1      |

| 0 | 0 | 1 | 0      |

• FF-T: ad ogni colpo di clock commuta o no a seconda del valore di T

• FF-D: ad ogni colpo di clock scrive 1 o 0 a seconda del valore di D.

## TABELLA RIASSUNTIVA

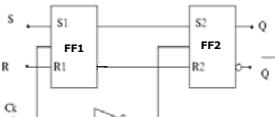

## FLIP-FLOP - MASTER/SLAVE

Il segnale di clock separa le variazioni dei dispositivi di memoria dall'assestamento dei circuiti combinatori.

Ck=0: FF1 disabilitato, FF2 abilitato, le uscite commutano e potenzialmente tutti i circuiti che seguono.

Ck=1: FF1 abilitato, FF2 disabilitato, le uscite sono stabili e FF1 si assesta in funzione del valore degli ingressi